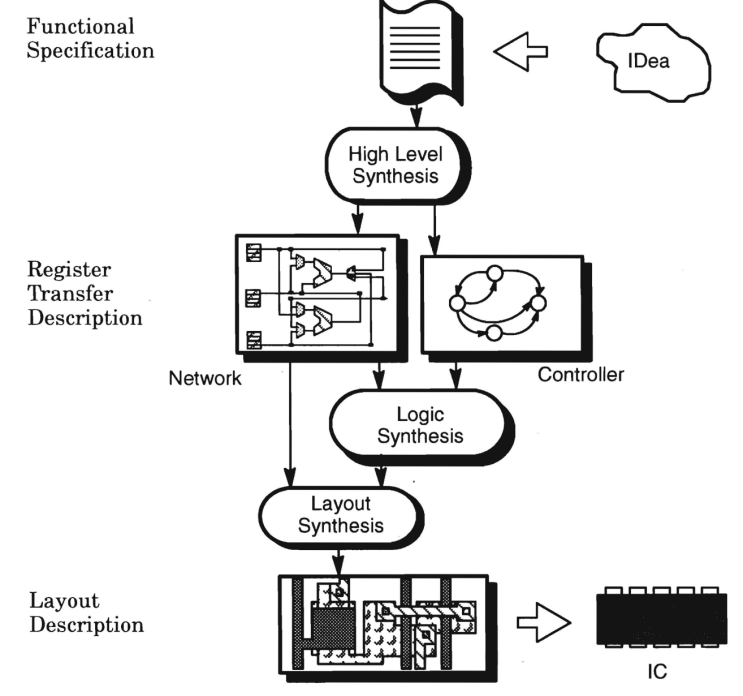

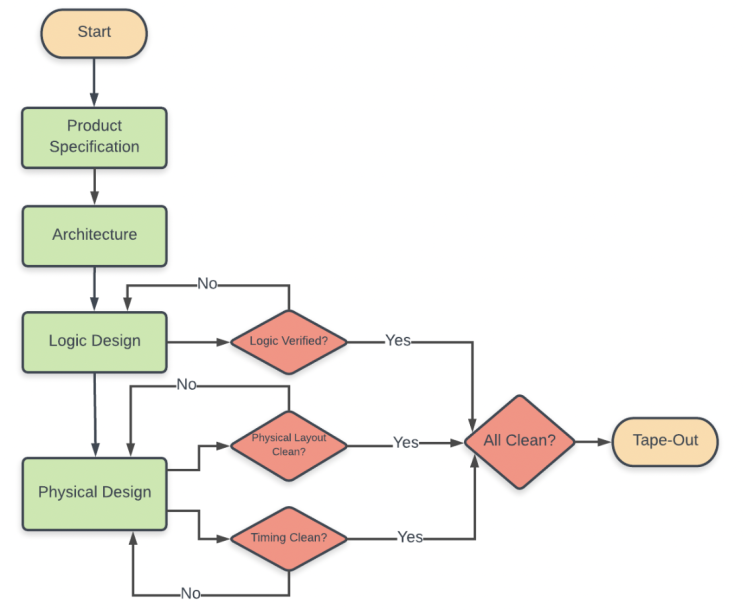

양산을 하려면, ASIC이라는 반도체를 만들어야 합니다. 설계회사에서 RTL이라는 파일로 시작해서 GDS라는 파일로 끝납니다. 이 과정을 RTL2GDS라고 합니다. 이 GDS를 공장에 전달하면, 공장은 Design Rule Check를 하고, 마스크를 만듭니다. 설계회사들은 이 마무리 단계를 Tape out이라고 합니다. ASIC Flow는 Architecture Design -> RTL Design -> Logic Synthesis -> Place & Route -> Signoff 이런식으로 진행을 합니다. 최적화되지 않은 아키텍쳐 설계로 기능 동작만 구현하고, Logic synthesis와 Place & Route를 해봤자 Signoff를 넘어갈 수 없습니다. EDA Tool은 그냥 RTL Code를 GDS Code로 바꿔주는 Code2Code Tool일 뿐입니다. 1) RTL 디자인이 Physical에 대한 고려가 안 되어있으면 2) 공정 라이브러리의 Variation이 너무 ...

원문링크 : EDA Tool(Synthesis, Place and Route)은 어떤식으로 회로 설계 최적화(Optimization)을 할까? 양산을 위한 반도체 설계

네이버 블로그

네이버 블로그 티스토리

티스토리 커뮤니티

커뮤니티