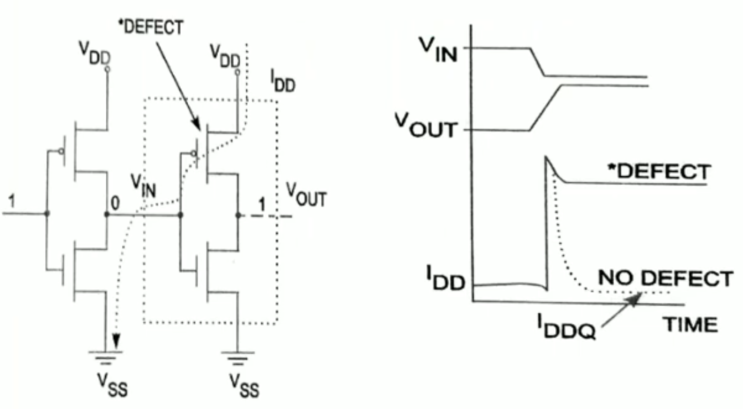

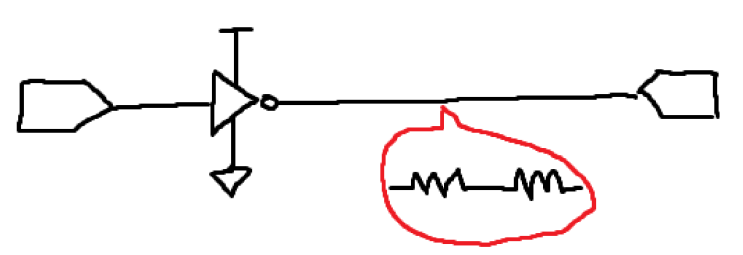

IDDQ란? 대기상태(Quiescent state)에서 공급전류(Idd)를 측정하는 회로 테스팅 방법론입니다. "회로의 신호 전환이 이뤄졌을 때, 순간 Static Current가 뜨겠지만, 그 이후엔 Static current가 0에 가까운 값이 나오는게 기본적인 CMOS입니다." 그런데 공정상에서 결함이 발생하면, 정적상태에서도 매우 큰 Static Current가 흐르게되고, 결국 칩이 정상작동하지 않게 됩니다. 기능 자체는 정상작동 할 수도 있는데, 전력 소비가 커지겠죠. 전력 소비가 만약 너무 크다 하면 기능도 정상 작동 안할 것이구요. Defect 예시입니다. Credit: https://eecs.ceas.uc.edu/~jonewb/iddq.pdf 용어 설명 : IDD: Current flow through VDD Q: Quiescent state IDDQ Testing: Detecting faults by monitoring IDDQ 회로의 신호를 전환시키지 않고 일정하...

원문링크 : IDDQ 테스팅: 정적 상태에서 흐르는 전류를 갖고 공정 결함을 검증하는 방법론

![[2021 마이 블로그 리포트] 블로그 빅데이터로 알아보는 '2021 내 블로그 스타일'](https://mblogthumb-phinf.pstatic.net/MjAyMTEyMTBfMTk3/MDAxNjM5MTQzNDAyOTY0.BUu-fi1MaGMNUdT0mF2RbCeMC8bUU3fcuI0lWrkYRlEg.EY2Enm72F-6RwO6-hJfeSdYJAw46bMB1BVWiLhscjM4g.PNG.gc_na/my_blog_report.png?type=w2)

네이버 블로그

네이버 블로그 티스토리

티스토리 커뮤니티

커뮤니티