![[Verilog, 디지털공학]X, Z, 차이, Metastability란? DRC란? [Verilog, 디지털공학]X, Z, 차이, Metastability란? DRC란?](https://blogimgs.pstatic.net/nblog/mylog/post/og_default_image_160610.png)

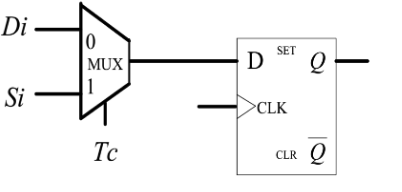

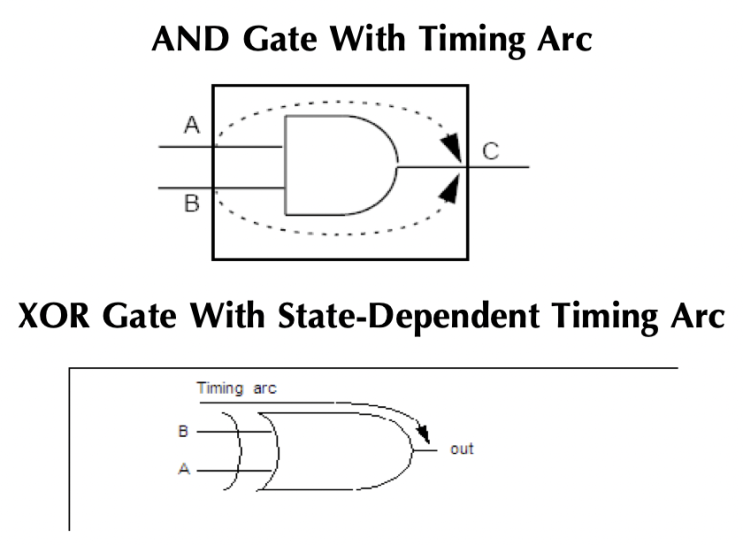

우선, wiki에 자세한 정보가 나와있으니, 참고하시길 바랍니다. https://en.wikipedia.org/wiki/Metastability_(electronics) X(don't care, Unknown) -> Z(High Impidance) -> Metastability 순으로 설명하겠습니다. Digital은 0과 1로 이루어져 있습니다. 우리가 진리표를 그릴 때, 어떤 입력이 들어오든 출력이 결정 되어있으면, 거기엔 X (don't care) 표시를 해줍니다. 입력에선 사실 이런걸 몰라도(?) 상관 없는데, 출력엔 이게 정말 중요합니다. 칩이 버그가 생길 수 있거든요. 반도체 설계로 밥벌이하는 사람들도 이거로 실수하고, 툴에서도 최대한 이런 문제(LINT)가 있다는걸 미리 알려주지만.. 툴도 찾지 못하고 설계..........

원문링크 : [Verilog, 디지털공학]X, Z, 차이, Metastability란? DRC란?

네이버 블로그

네이버 블로그 티스토리

티스토리 커뮤니티

커뮤니티