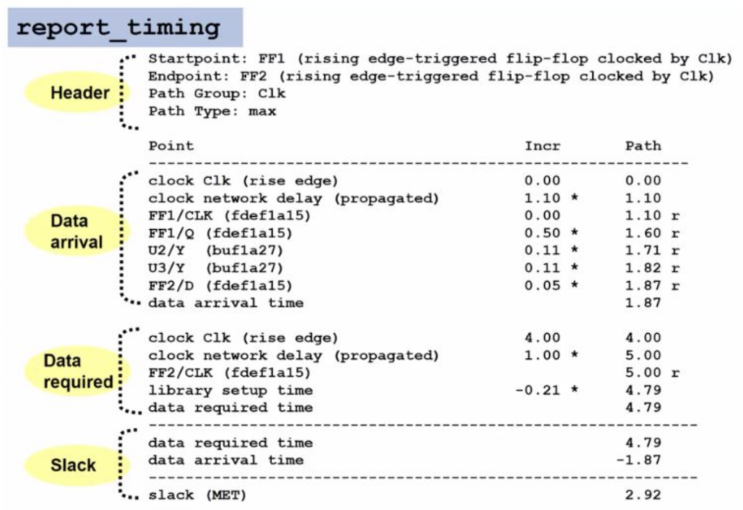

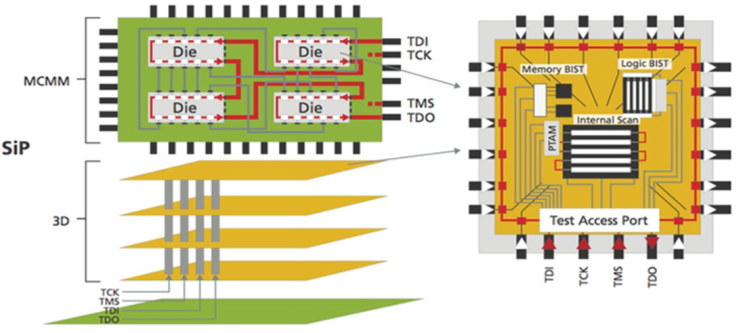

설계검증을 하려면 Function과 Physical을 봐야할 줄 알아야합니다. Physical에서 가장(?) 중요한게 Function 동작을 위한 Timing 제약 조건을 맞춰야 하는 것입니다. Timing 분석으로 대표적인건 Dynamic Timing Analysis, Static Timing Analysis, Monte Carlo simulation등이 있습니다. DTA는 너~무 많은 시간을 소요하구요. Monte carlo sim은 일반적인 경우에선 사용되지 않습니다... (제가 써본적이 없습니다..) 결국 STA로 Timing 검증을 합니다. STA Engineer라면 공정 라이브러리 분석, SDC clean, Timing path 분석, Timing Close를 할 줄 알아야하는데요. 펀더멘탈부터 시작해보겠습니다. 디지털논리회로에 timing이 뭐냐? Circuit level에서 Timing = Cell delay + Net delay 각 Delay를 input transi...

#verilog

#공정

#반도체

#반도체설계

#설계

원문링크 : STA Engineer (Static Timing Analysis) 엔지니어가 타이밍을 볼 때. 라이브러리 캐릭부터 DTA까지

네이버 블로그

네이버 블로그 티스토리

티스토리 커뮤니티

커뮤니티