![[반도체 이론] CMOS 소자 공학 Side Effect(2'nd Effect) [반도체 이론] CMOS 소자 공학 Side Effect(2'nd Effect)](https://mblogthumb-phinf.pstatic.net/MjAyMjA5MTVfMjY1/MDAxNjYzMjQxNzk1MjMz.TpRoghZHlekd1bEK0PBfOjAlVqKaON2FdtmvxL7vER4g.XFOVh0Z9J2P6rIaSnFgN2_OH7KYLH-V1THvpGIu483Ug.PNG.mjs9726/%B1%D7%B8%B21.png?type=w2)

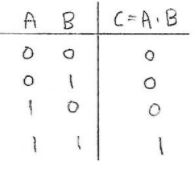

CMOS 소자공학 CMOS 소자공학 2'nd Effect 2'nd Effect 반도체 소자가 작아지며(집적화)되며 생기는 부작용(Side Effect) CMOS 소자 정적 소모 전류 및 Delay 개선 방법 •Reducing Threshold Voltage •저 전압으로 On/Off가 가능 •의도하지 않은 전압으로 On/Off 될 수 있다. •Increasing Channel Width •더 많은 Carrier가 움직일 수 있도록 Channel Width 증가. •3D 구조의 FINFET과 같은 공정으로 전환. •Increasing Vdd •증가로 인해 동작 속도는 증가, 전력 소모 고려 필요 •Reducing Short channel effect •MOSFET에서 발생하는 NONIDEAL 효과 개선 CMOS 소자 Side Effect 종류 Short Channel Effect MOSFET 소자의 크기가 Scale Down 되어가며, 생기는 Side Effect -Punch Thro...

#CMOS

#소자집적화

#반도체소자집적화문제

#반도체소자부작용

#반도체문제

#vth

#Sideeffect

#punchthrough

#pnjunction

#leakage

#hotcarrierinjection

#DIBL

#CMOS소자공학

#집적화문제

원문링크 : [반도체 이론] CMOS 소자 공학 Side Effect(2'nd Effect)

![[반도체 공정실습] Etch 용어 정리](https://mblogthumb-phinf.pstatic.net/MjAyMTAxMjRfMTAz/MDAxNjExNDkyNjkzODAy.nqoLN_hjUVTQ2sgOxU7EwiL4bgtByhYLOsW_IDnvEBIg.2rYqtsWKe0pFhadfnlJaB3SIV49Eb95_qWGO3kdubZog.PNG.mjs9726/image.png?type=w2)

![[서울 여행] 노들섬, 새로운 불꽃축제 명소 되다!<불꽃축제 명당,노들섬 추천, 노들섬 가는법, 여의도 불꽃축제>](https://mblogthumb-phinf.pstatic.net/MjAxOTEwMzBfMjE4/MDAxNTcyNDMzNzk1Nzcx.-374mq2dxrIgubzHri7H-J2SIpPhdok1BjMZJCagMLMg.5nX2tTHfLHFplJuLIvctJneZ4nyaeZxLuCFgPmCjTQ4g.JPEG.mjs9726/20191005_203644.jpg?type=w2)

네이버 블로그

네이버 블로그 티스토리

티스토리 커뮤니티

커뮤니티