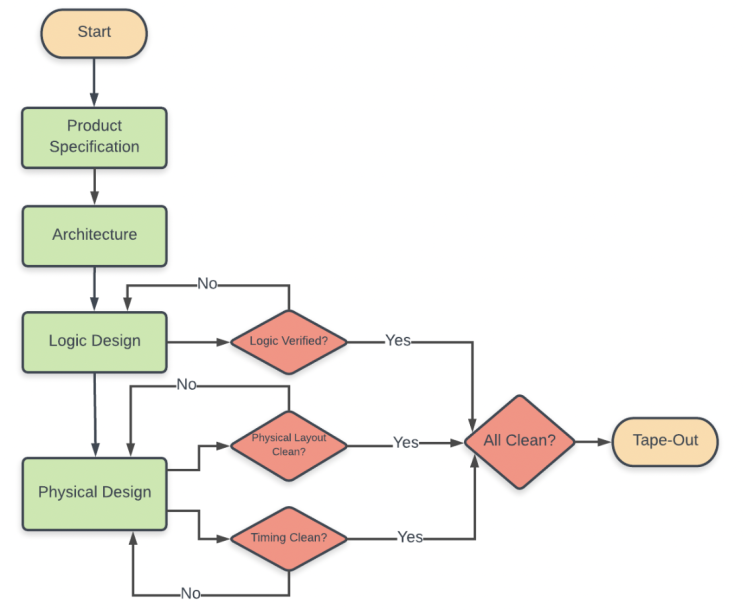

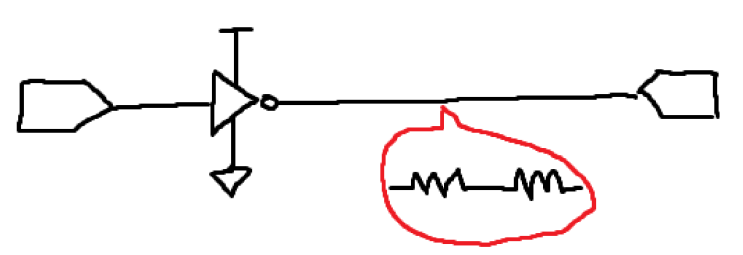

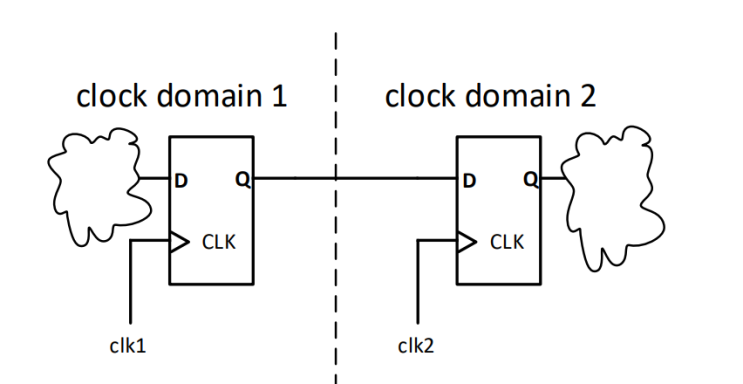

Clock Tree Synthesis(CTS)는 디지털 회로에서 사용되는 하나의 기술입니다. 하나의 Chip에는 수십만, 수십억 개의 Flip-Flop이 있습니다. 1.이 Flip flop을 Triggering 시키는 신호는 clock입니다. 2.Logic Design에서는 앞단의 Flip flop이 뒷단에 flip flop에 data를 넘겨주는식으로 설계를 합니다. 3.근데 이 Chip을 실제 웨이퍼에 그릴 Physical layout을 하면, 각 Flip-Flop의 clock pin과 Clock Source와 각각 거리가 달라집니다. Flip flop이 Trigger가 전부 다른 타이밍에 일어나게 됩니다. clock source에서 신호를 출력할 때 clock pin에서 입력 받는 시간을 Clock Latency라고 부릅니다. 3번에 말한것처럼 각 Flip flop은 각기 다른 Clock Latency를 갖습니다. 각 Flip flop간 clock latency의 차이를 Cloc...

원문링크 : Clock Tree Synthesis(CTS)의 기본 알고리즘, H-Tree, Fishbone, Mesh, Low Power CTS

네이버 블로그

네이버 블로그 티스토리

티스토리 커뮤니티

커뮤니티