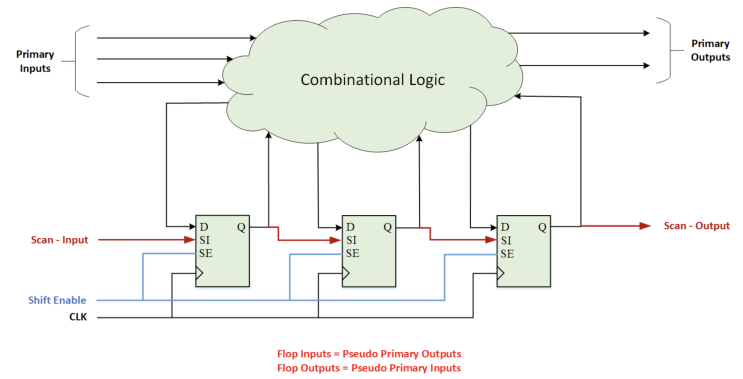

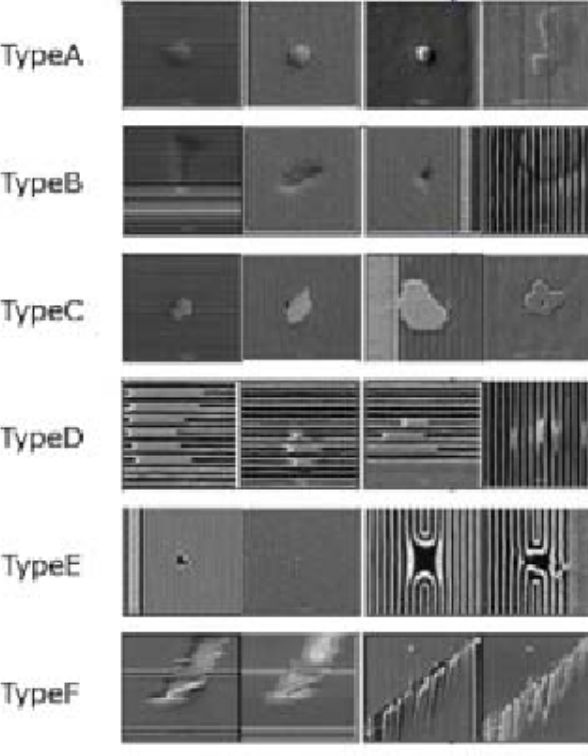

Overview DFT라고 불리는 Design For Testability는 디지털 회로 설계에서 사용되는 방법론입니다. 논리 회로 설계를 이상적으로 구현하였더라도, 공정 결함으로 문제있는 반도체 칩은 발생 할 수 있습니다. 뭔가 살짝 얇게 들어가거나, 더 두껍게 들어가면 이런게 결함이 되죠. 이런 칩들을 높은 정확도로 빠르게 찾아내기 위해 "검증을 위한 설계"를 회로에 넣습니다. SCAN Design은 DFT의 대표적인 설계 기법입니다. 이는 회로 내 모든 플립플롭을 몇 개의 체인으로 연결하고, "테스트 시에는 테스트 장비의 입력을 넣고 출력을 뺄 수 있게" 하는 방법론입니다. 이렇게 하여 테스트 벡터를 쉽게 인가하고 테스트 응답을 관측 할 수 있습니다. 문제는, 회로의 크기가 매우 커지고 복잡도가 증가함에 따라, "SCAN Chain의 물리적인 길이가 너무 길어지게 됩니다. 이는 테스트 벡터 전달 시간 증가, Clock Frequency를 낮춰야 하는 문제들이 생깁니다. 이런 문...

원문링크 : DFT에서 Pipe register의 역할

![[ML/DL] Sigmoid Function이란?](https://mblogthumb-phinf.pstatic.net/MjAyMzA0MTBfMTUy/MDAxNjgxMTM3MDQ1MTc4.cDymRNw923Q9UADpp5UqiKhIjy4TkmMS7eBK7Avh_-Yg.AjeQzXgd4ecz-eXYbfTYTdM_yU9TW4l-XxcXsvXx2rIg.PNG.gc_na/image.png?type=w2)

![[공대생 일상] 엔지니어는 휴무일때 뭐할까.log](https://mblogthumb-phinf.pstatic.net/MjAyNDAzMTFfMTQz/MDAxNzEwMTU5ODY3MjUz.NAWTWaU1FkT4SGjp2m2eMhjox5LYeWBqfi29rL9T9vcg.bJ74Xa1c1YJmvCclzhG51vNTJx1NI270K6R02JrBeWYg.JPEG/output_1096886027.jpg?type=w2)

네이버 블로그

네이버 블로그 티스토리

티스토리 커뮤니티

커뮤니티