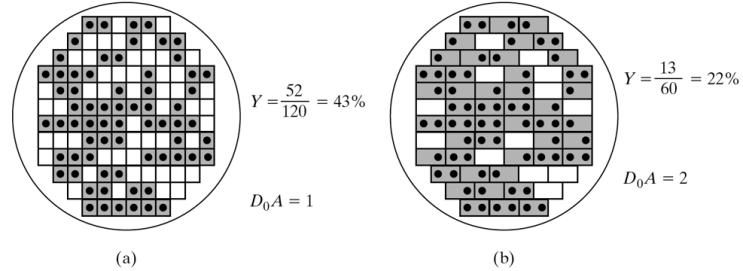

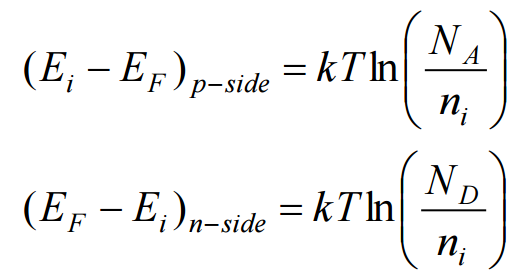

이번 포스팅은 패키징 공정의 마지막인 Relation between Yield & Area와 Yield를 Modeling하는 방법에 대해 알아보겠습니다. 이번 포스팅을 마지막으로 반도체 8대 공정에 대해 모두 학습했습니다. 1. Relation between Yield & Area Introduction to Microelectronic Fabrication, 2nd Ed., R. C. Jaeger 위 그림은 면적에 대한 수율에 대해 비교한 그림입니다. 불량 Die의 Contentration은 같다고 가정했을 때 Chip size가 작을수록 웨이퍼의 수율이 높은 것을 확인할 수 있습니다. wafer의 크기를 고정하고 die 크기를 줄이면 wafer에서 전체 die가 차지하는 부피가 커집니다. Wafer 위에 defect 수가 1개라고 할 때, wafer 위에 1개의 die만 존재한다면 sort yield(λ)는 0%이지만, wafer 위에 100개의 die가 존재한다면 그 중 한 개...

#반도체

#반도체8대공정

#반도체공정

#반도체공정이론

#반도체공정재료

원문링크 : 반도체 공정 52장(Relation between Yield & Area / Yield modeling)

![[익선동 맛집] 간장게장 맛집 평해옥](https://mblogthumb-phinf.pstatic.net/MjAyMzEyMjNfNjgg/MDAxNzAzMjU4MTg0MDMx.EuThC8Q-XsF_7sZnwalAhLIwR9Xdi3JZKsKEZN8Uf84g.Y5Hnid_ANxQ2RuuFEbZsl0EXLrb8QUND9tM5gN4hquEg.JPEG.jgc990203/IMG_1362.jpg?type=w2)

![[성신여대역 맛집] 폴라니포케 성신여대점](https://mblogthumb-phinf.pstatic.net/MjAyMzA1MTZfMTI5/MDAxNjg0MjE1NzE1MDQ1.rbb1jNw0bYOC-EZC3ycFes5fs8SeCM1fkfyGbArbFncg.j_UkSuI6z7zIAN5WWwnCyPe212ulihv_k9AH2UYfR-0g.JPEG.jgc990203/IMG_4232.jpg?type=w2)

네이버 블로그

네이버 블로그 티스토리

티스토리 커뮤니티

커뮤니티